## FROM NANO-SCALE TO TERA-SCALE An Intel Perspective

Jerry Bautista, PhD Co-Director Tera-scale Program Intel Microprocessor Research

### Corporate Technology Group (CTG) Strategic Objectives

Conduct world-class research

Deliver innovative technologies from concept to product adoption

Collaborate with industry via standards, alliances and evangelism

Engage worldwide for the best research and technology

### **Research at Intel**

### Nearly 1000 researchers

15 locations worldwide

Innovative research models

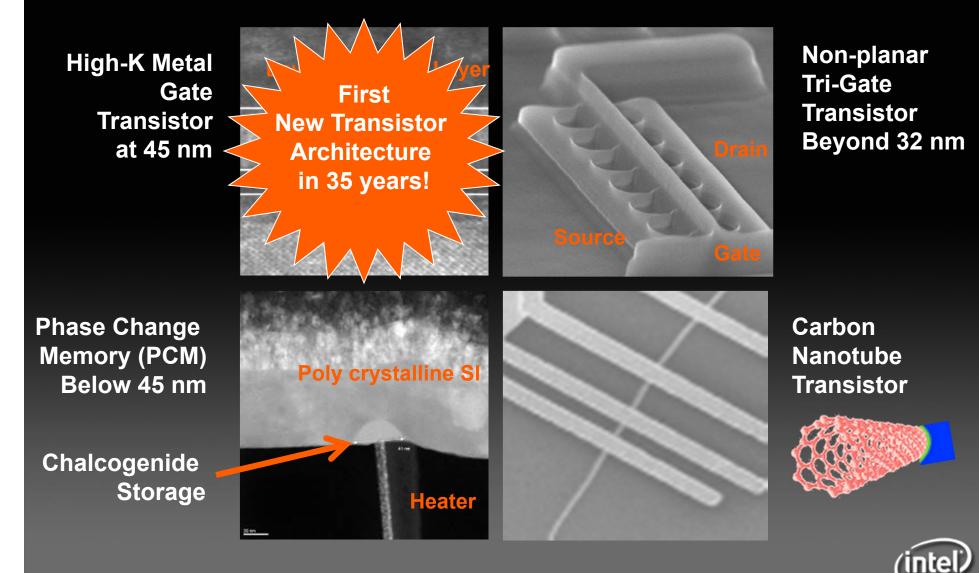

### Nanodevice R&D

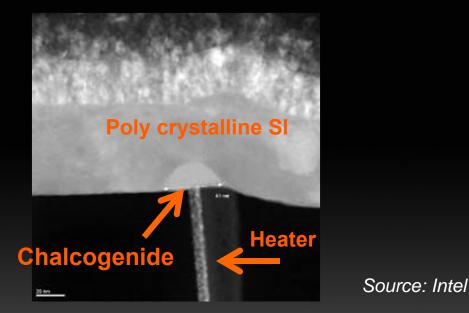

Source: Intel

# Phase Change Memory PCM Cell

- Non volatile

- Bit alterable

- Very fast and low power

- Scalable well below 45 nm

- High endurance (>100M writes)

- Partners

- Ovonyx Since 2000

- R&D with ST since 2003

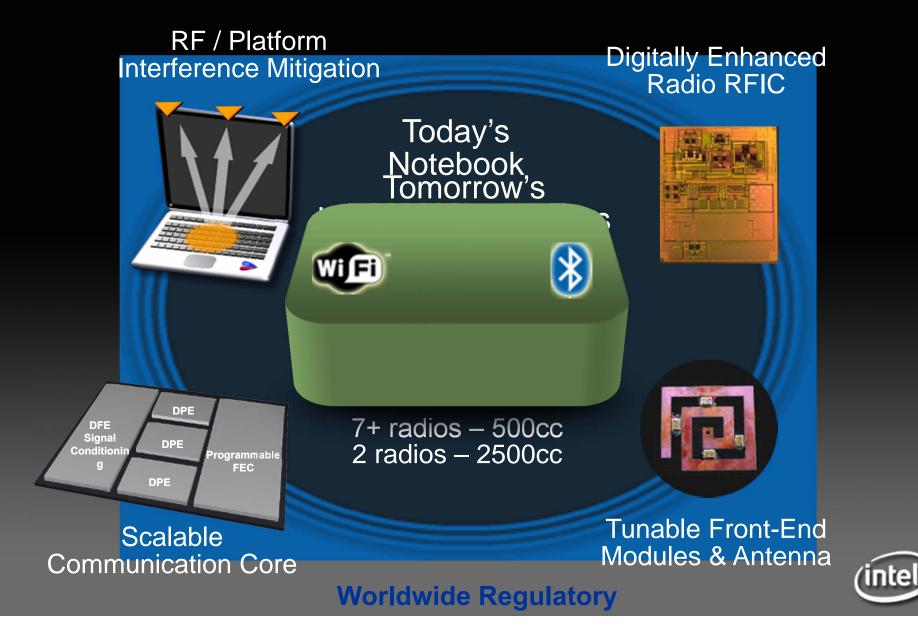

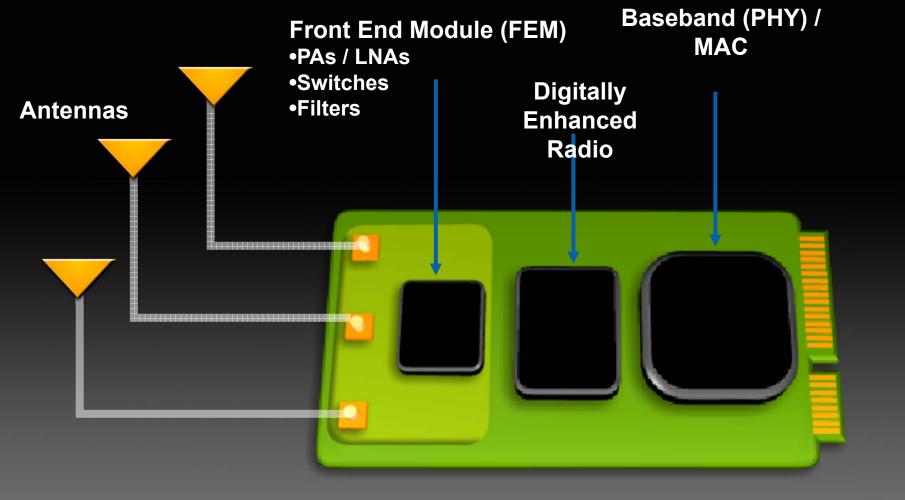

### **Digital Multi-Radio Technology**

### **Digital Multi-Radio Components**

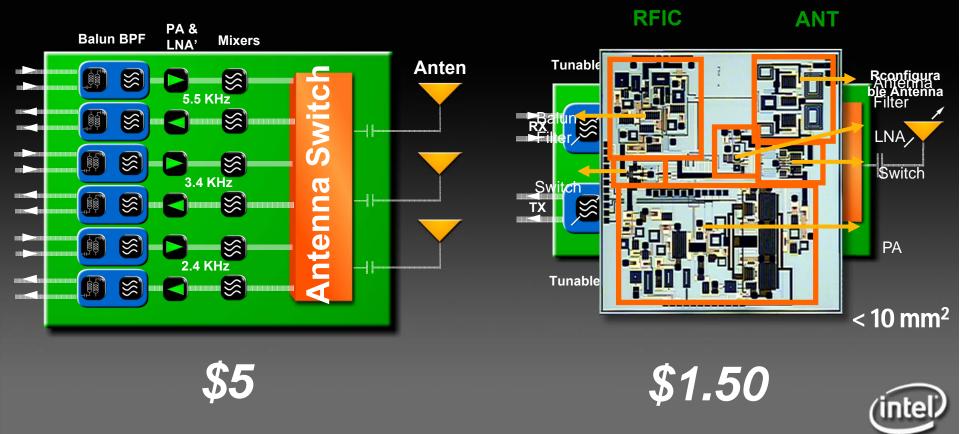

## Conventional FEM v. Flexible FEM

Today's Conventional Multi-Standard (WiFi a/b/g) + WiMax FEM Next Generation Conventional Multi Standard (WiFi a/b/g) + WiMax FEM

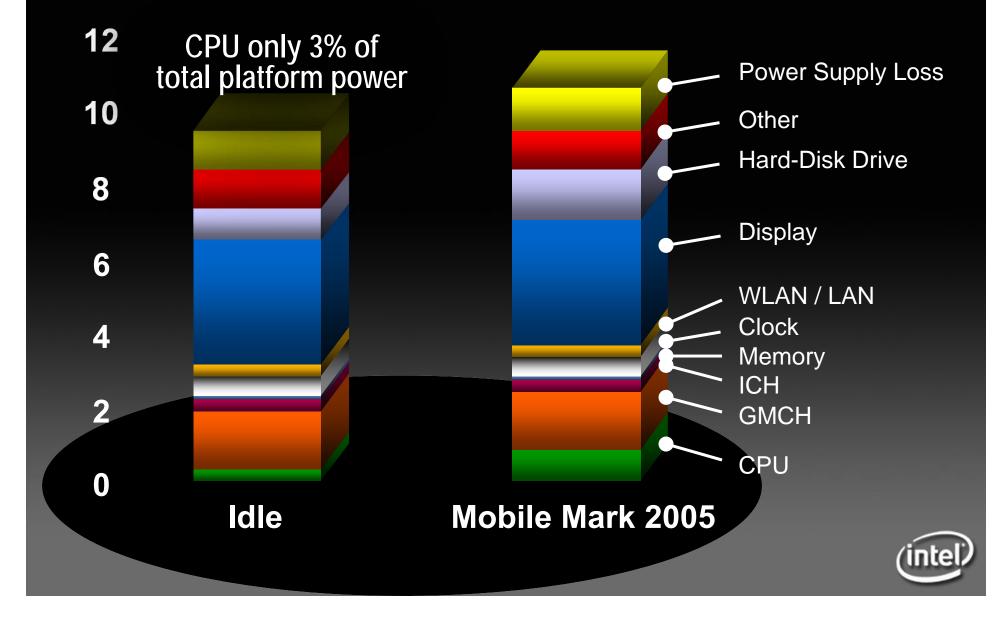

### Energy Efficiency: Average vs. Idle

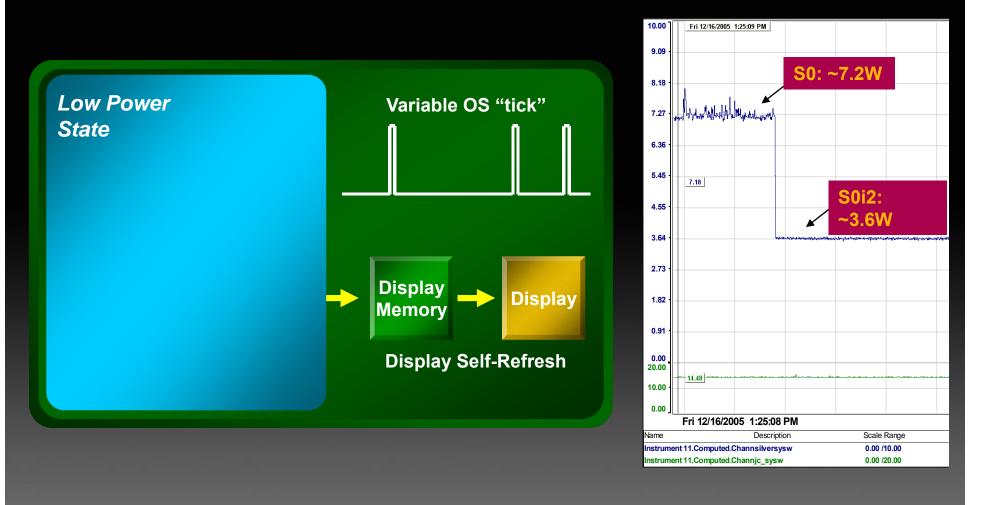

### Display Self-Refresh Extended Idle Mode

### **Power Delivery Inefficiency**

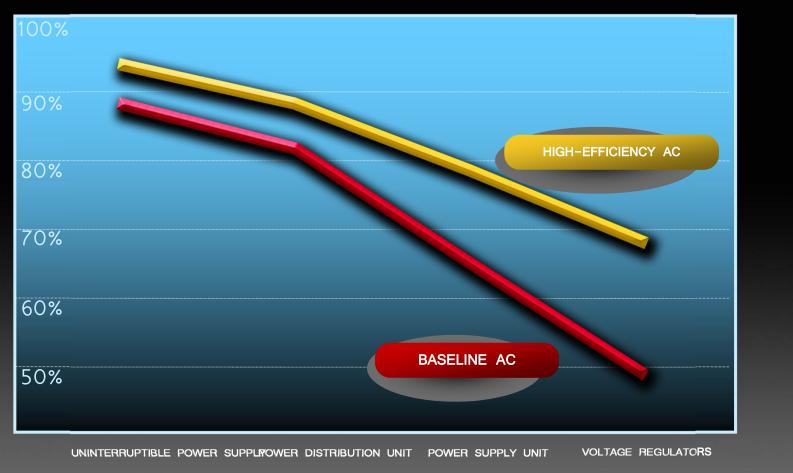

CUMULATIVE DATACENTER POWER DELIVERY EFFICIENCY

Source: Intel

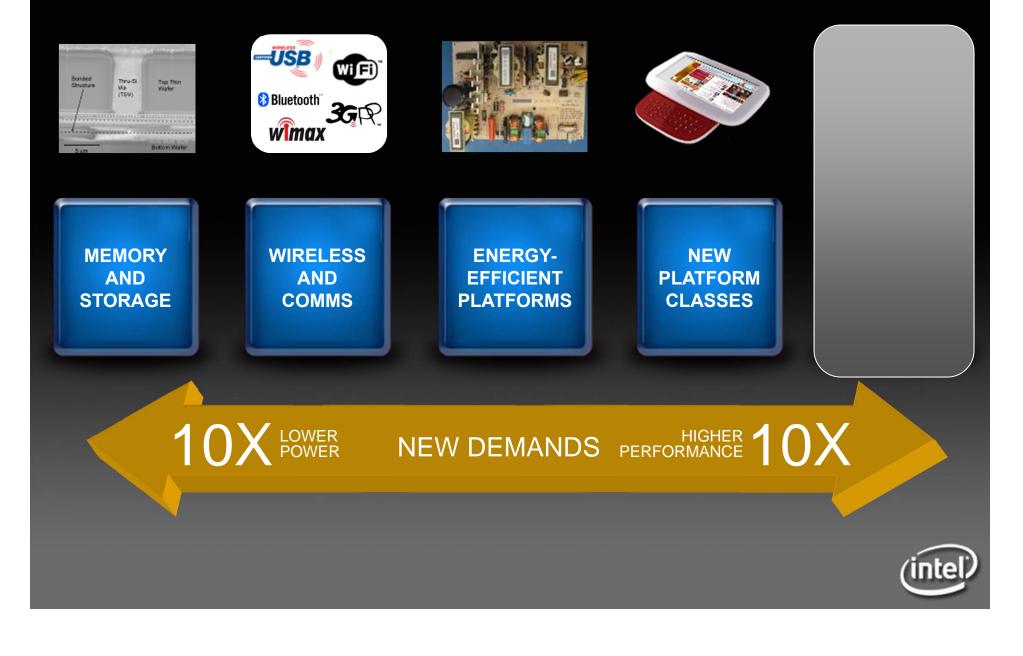

### Enabling Full Internet in Your Pocket

### **Enabling The Full Internet in Your Pocket**

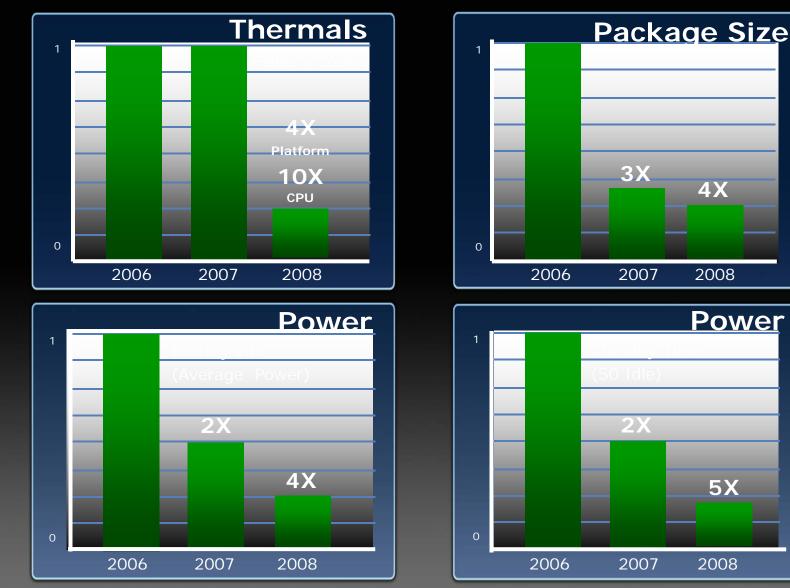

(Charts Shows CPU + Chipset\*)

\* Both 2006 and 2007 average power number are measured based on MPG products. 2007 is a derivative of Dothan, again measured from MPG and remeasured on smaller package. Average power is the power consumed by the CPU from the core rail, in adaptive mode and low frequency mode (LFM) while running MobileMark\* 2005 office productivity benchmark on a median leakage device. 2008 and beyond data are forecasted based on current engineering plan and anticipated technological improvement. All plans, features and dates are preliminary and subject to change without notice.

ne

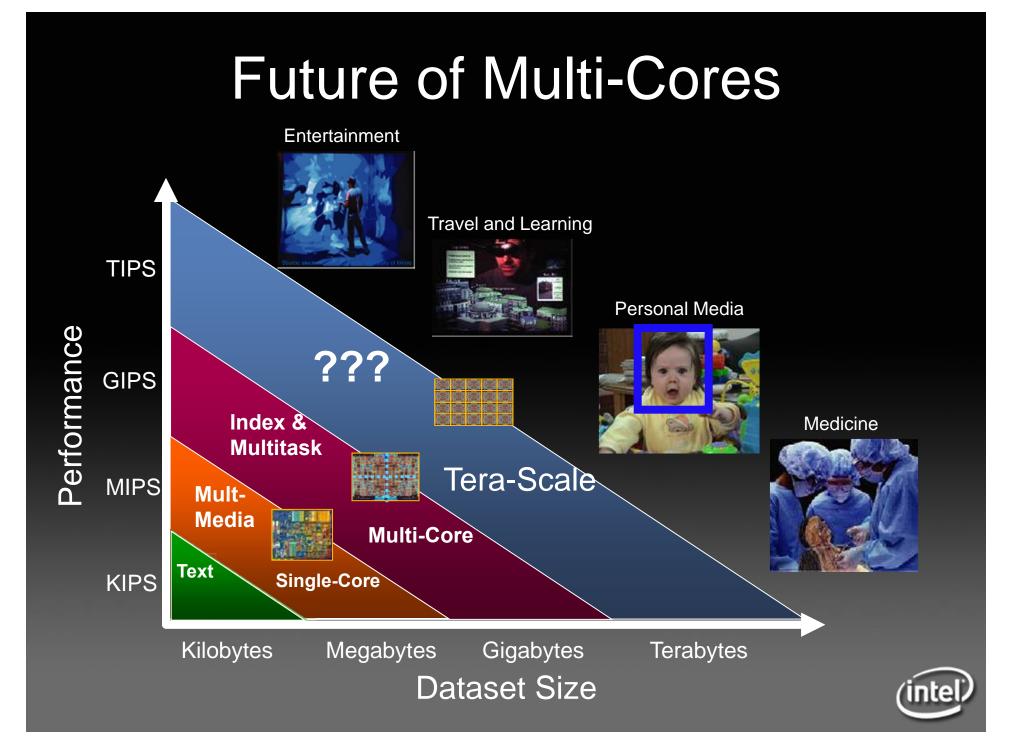

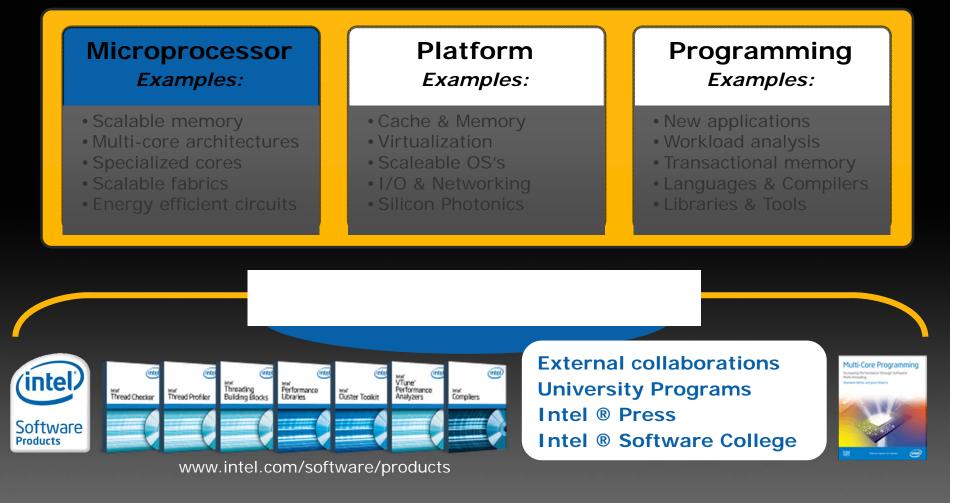

# Intel Tera-scale Computing Research

#### More than 100 projects worldwide

Intel Higher Education on track to impact 400 university curricula by end of 2007  $\rightarrow$  Focus on Parallel Programming

### What Future Chips Might Look Like: From a few large cores to many simpler cores

Optimized for speed

Optimized for performance/watt

Shared Local Cache Cache Streamlined IA Core

Pentium® processor era chips optimized for raw speed on single threads. Pipelined, out of order execution. Today's chips use cores which balance single threaded and multi-threaded performance 5-10 years: 10s-100s of IA cores, interconnect network, Some non-IA accelerators

## Other reasons for many cores

Sleep

Sleep

#### Integrated Network

•Higher b/w & lower latency compared to SMP

Spare

Spare

Spare

IA

Sleep

Fine grained power management

Voltage scaling at core level

• Yield & Resiliency Spare cores & binning Hybridization

Integration of fixed function accelerators

es

Improved virtualization another likely benefit of many core

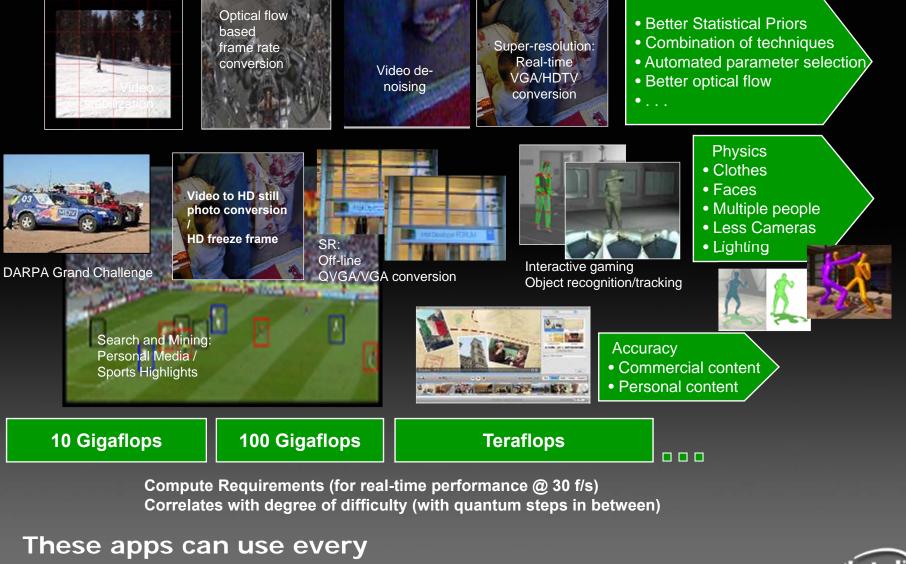

### What to do with the performance?

available FLOP!

### Ray Tracing – photo realism

**3D Graphics Rendering**

shadows, etc.

Today's Game Graphics Processing : Each triangle is processed independently in layers, foreground, background,

Ray Tracing – physically simulating light, compute intensive, collision of light rays with objects, reflections, refractions.

Can be used to detect body-to-body collisions as well

(intel)

#### Stats:

Render Time: 30 minutes Processor: P4 3Ghz RAM: 512MB Renderer: Mental Ray DOF: Simulated in Photoshop

~3000 FLOPs/Ray Segment ~1500 Bytes/Ray Segment

Rendering consumes ~90% of system resources.

### Model-Based Computing

- Representing and processing data using digital "concepts" ullet

- Composed of mathematical rules and variables that approximate reality

- Allow computers to recognize, manipulate, and represent things and ideas

Facial

Model

Climate Model

Atomic Model

Cloth Body Model Model

Financial Model

Behavioral Model

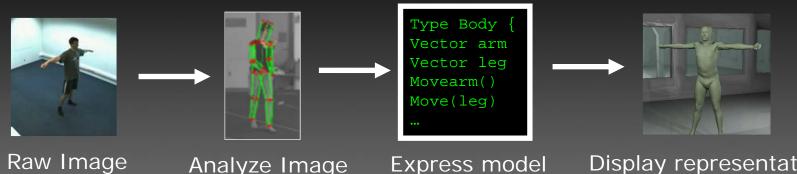

### Example: Modeling body motion

#### **Display representation**

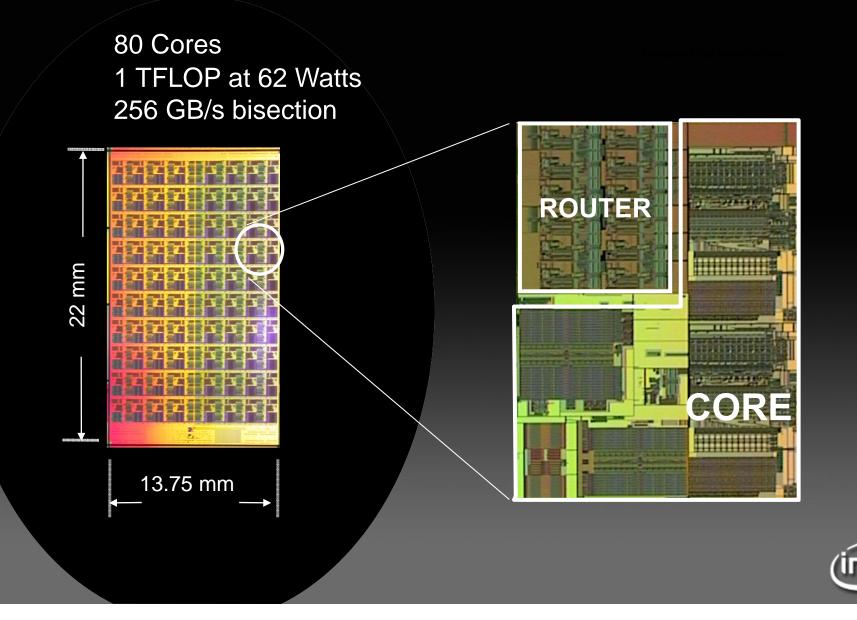

### Polaris: Tera-Scale Prototype

### Tera-scale Software Opportunities and Risks

Reduced Productivity in Parallel Programming

- Decomposition Difficult to compose parallel programs

- Data races Bugs increase exponentially with degree of parallelism

- Load Balance Trouble keeping all processors busy

Major challenges in enabling "easy" parallel programming - a **major** focus area for Research

## **EVERYTHING MATTERS**

Energy. Performance. Storage. I/O. Mobility. Security. Reliability. Applications. Provisioning. Cost.